# Lecture Notes in Computer Science

3659

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Josyula R. Rao Berk Sunar (Eds.)

# Cryptographic Hardware and Embedded Systems – CHES 2005

7th International Workshop Edinburgh, UK, August 29 – September 1, 2005 Proceedings

#### Volume Editors

Josyula R. Rao IBM T.J. Watson Research Center 19 Skyline Drive, Hawthorne, NY 10532, USA E-mail: jrrao@us.ibm.com

Berk Sunar Worcester Polytechnical Institute Department of Electrical and Computer Engineering 100 Institute Road, Worcester, MA 01609, USA E-mail: sunar@wpi.edu

Library of Congress Control Number: 2005931119

CR Subject Classification (1998): E.3, C.2, C.3, B.7, G.2.1, D.4.6, K.6.5, F.2.1, J.2

ISSN 0302-9743

ISBN-10 3-540-28474-5 Springer Berlin Heidelberg New York ISBN-13 978-3-540-28474-1 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© International Association for Cryptologic Research 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11545262 06/3142 543210

## **Preface**

These are the proceedings of the 7th Workshop on Cryptographic Hardware and Embedded Systems (CHES 2005) held in Edinburgh, Scotland from August 29 to September 1, 2005. The CHES workshop has been sponsored by the International Association for Cryptologic Research (IACR) for the last two years.

We received a total of 108 paper submissions for CHES 2005. The double-blind review process involved a 27-member program committee and a large number of external sub-referees. The review process concluded with a two week discussion process which resulted in 32 papers being selected for presentation. We are grateful to the program committee members and the external sub-referees for carrying out such an enormous task. Unfortunately, there were many strong papers that could not be included in the program due to a lack of space. We would like to thank all our colleagues who submitted papers to CHES 2005.

In addition to regular presentations, there were three excellent invited talks given by Ross Anderson (University of Cambridge) on "What Identity Systems Can and Cannot Do", by Thomas Wille (Philips Semiconductors Inc) on "Security of Identification Products: How to Manage", and by Jim Ward (Trusted Computing Group and IBM) on "Trusted Computing in Embedded Systems". It also included a rump session, chaired by Christof Paar, featuring informal talks on recent results.

The focus of CHES 2005 was similar to that of the earlier CHES workshops with the addition of a few new topics of emerging interest among which were smart card attacks and architectures, tamper resistance on the chip and board level, true and pseudo random number generators, special-purpose hardware for cryptanalysis, embedded security, cryptography for pervasive computing (e.g., RFID, sensor networks), device identification, non-classical cryptographic technologies, and side channel cryptanalysis. Special attention was paid to trusted computing platforms.

Special compliments go out to Colin D. Walter, the general chair and local organizer of CHES 2005, who brought the workshop to the beautiful historic town of Edinburgh, Scotland making it as much of a cultural event as a stimulating technical gathering. Christof Paar held the publicity Chair of CHES and was helpful at all stages of the organization. We would like to thank our corporate sponsors Cryptography Research Inc., escrypt GmbH, Gemplus, IBM, and RSA Security, who made it possible to have a lively event with their generous contributions. We would like to thank our dedicated webmaster Jens-Peter Kaps for maintaining the CHES website and review system even when he was travelling. Finally, we would like to thank the CHES steering committee members for giving us the honor of being part of such an influential conference.

# 7th Workshop on Cryptographic Hardware and Embedded Systems

August 29 - September 1, 2005, Edinburgh, Scotland http://www.chesworkshop.org/

# Organizing Committee

## **Program Committee**

| Ross Anderson               | Cambridge University, UK                                 |

|-----------------------------|----------------------------------------------------------|

| Mohammed Benaissa           | The University of Sheffield, UK                          |

| Suresh Chari                | IBM T.J. Watson Research Center, USA                     |

| Kris Gaj                    | George Mason University, USA                             |

| Louis Goubin Uni            | versité de Versailles-St-Quentin-en-Yvelines, France     |

| Jorge Guajardo              | Infineon Technologies, Germany                           |

| Çetin Kaya Koç              | Oregon State University, USA                             |

| Peter Kornerup              | University of Southern Denmark, Denmark                  |

| Pil Joong Lee               | Postech, South Korea                                     |

| David Naccache              | Gemplus, France and                                      |

|                             | Royal Holloway, University of London, UK                 |

| Elisabeth Oswald            | Graz University of Technology, Austria                   |

| Christof Paar               | Ruhr-Universität Bochum, Germany                         |

| Daniel Page                 | University of Bristol, UK                                |

| Bart Preneel                | Katholieke Universiteit Leuven, Belgium                  |

| Pankaj Rohatgi              | IBM T.J. Watson Research Center, USA                     |

| Ahmad Sadeghi               | Ruhr-University Bochum, Germany                          |

| Kouichi Sakurai             | Kyushu University, Japan                                 |

| David Samyde                | FemtoNano, France                                        |

| Erkay Savaş                 | Sabanci University, Turkey                               |

| Werner Schindler            | Bundesamt für Sicherheit                                 |

|                             | in der Informationstechnik, Germany                      |

| Jean-Pierre Seifert         | Intel, USA                                               |

| Nigel Smart                 | University of Bristol, UK                                |

| Francois-Xavier Standaert . | $\ldots\ldots$ Université Catholique de Louvain, Belgium |

#### VIII Organization

## Steering Committee

#### **External Referees**

Onur Aciiçmez Dakshi Agrawal Mehdi-Laurent Akkar Roberto Avanzi Murat Avdos Yoo Jin Baek Lelia Barlow Lejla Batina Chevallier-Mames Benoit Guido Bertoni Régis Bevan Mike Bond Eric Brier Julien Brouchier Christophe De Cannière Dario Carluccio Laurent Caussou Juyoung Cha Herve Chabanne Nam Su Chang Kookrae Cho Mathieu Ciet Jolvon Clulow Jean-Sbastien Coron

Nicolas Courtois Colin van Dyke Serdar S. Erdem Martin Feldhofer Patrick Felke Wieland Fischer Jacques J.A. Fournier Patrick George Christophe Giraud Robert Granger Johann Großschädl Adnan Gutub Ghaith Hammouri Dong Guk Han Helena Handschuh Oliver Hauck Alireza Hodiat Tetsuva Izu Mark Jung Charanjit Jutla Deniz Karakoyunlu Paul Karger Manabu Katagi Alisher Anatolyevich

Kholmatov Tae Hvun Kim Minho Kim Shinsaku Kiyomoto François Koeune Sandeep Kumar Klaus Kursawe Soonhak Kwon Gerard Lai Joe Lano Peter Leadbitter Hyang-Sook Lee Jung Wook Lee Kerstin Lemke HuiYun Li Marco Macchetti François Macé Stefan Mangard Marian Margraf Nele Mentens Atsuko Miyaji Christophe Mourtel Elke de Mulder Robert Mullins

Michael Neve Richard Noad Francis Olivier Gerardo Orlando Siddika Berna Ors Pascal Paillier Fabrice Pautot Matthew Parker Eric Peeters Jan Pelzl Gilles Piret Thomas Popp Axel Poschmann Christine Priplata Kumar Ranganathan Nalini Ratha Arash Revhani-Masoleh

Gaël Rouvroy

Andy Rupp Reiner Sailer Junichiro Saito Rvuichi Sakai Yasuvuki Sakai Kazuo Sakiyama Gökay Saldamlı Hisayoshi Sato Akashi Satoh Daniel Schepers Jörg Schwenk Kai Schramm Jong Hoon Shin Jamshid Shokrollahi Nicolas Sklavos Sergei Skorobogatov Colin Stahlke Martijn Stam

Makoto Sugita Katsuyuki Takashima Stefan Tillich Michael Tunstall Shigenori Uchuvama Guy Vandenbosch Ihor Vasylstov Frederik Vercauteren Karine Villegas Camille Vuillaume Andre Weimerskirch Claire Whelan Christopher Wolf Johannes Wolkerstorfer Thomas Wollinger Yeon Hyeong Yang Jeong Il Yoon Young Tae Youn

## Previous CHES Workshop Proceedings

- CHES 1999: Çetin K. Koç and Christof Paar (Editors). Cryptographic Hardware and Embedded Systems, vol. 1717 of Lecture Notes in Computer Science, Springer-Verlag, 1999.

- CHES 2000: Çetin K. Koç and Christof Paar (Editors). Cryptographic Hardware and Embedded Systems CHES 2000, vol. 1965 of Lecture Notes in Computer Science, Springer-Verlag, 2000.

- CHES 2001: Çetin K. Koç, David Naccache, and Christof Paar (Editors).

Cryptographic Hardware and Embedded Systems CHES 2001, vol. 2162

of Lecture Notes in Computer Science, Springer-Verlag, 2001.

- CHES 2002: Burton S. Kaliski, Çetin K. Koç, and Christof Paar (Editors). Cryptographic Hardware and Embedded Systems – CHES 2002, vol. 2523 of Lecture Notes in Computer Science, Springer-Verlag, 2002.

- CHES 2003: Colin D. Walter, Çetin K. Koç, and Christof Paar (Editors). Cryptographic Hardware and Embedded Systems CHES 2003, vol. 2779 of Lecture Notes in Computer Science, Springer-Verlag, 2003.

- CHES 2004: Marc Joye and Jean-Jacques Quisquater (Editors). Cryptographic Hardware and Embedded Systems CHES 2004, vol. 3156 of Lecture Notes in Computer Science, Springer-Verlag, 2004.

# Table of Contents

# Side Channels I

| Resistance of Randomized Projective Coordinates Against Power<br>Analysis                                        |     |

|------------------------------------------------------------------------------------------------------------------|-----|

| William Dupuy, Sébastien Kunz-Jacques                                                                            | 1   |

| Templates as Master Keys  Dakshi Agrawal, Josyula R. Rao, Pankaj Rohatgi, Kai Schramm                            | 15  |

| A Stochastic Model for Differential Side Channel Cryptanalysis  Werner Schindler, Kerstin Lemke, Christof Paar   | 30  |

| Arithmetic for Cryptanalysis                                                                                     |     |

| A New Baby-Step Giant-Step Algorithm and Some Applications to                                                    |     |

| Cryptanalysis  Jean Sébastien Coron, David Lefranc, Guillaume Poupard                                            | 47  |

| Further Hidden Markov Model Cryptanalysis  P.J. Green, R. Noad, N.P. Smart                                       | 61  |

| Low Resources                                                                                                    |     |

| Energy-Efficient Software Implementation of Long Integer Modular<br>Arithmetic                                   |     |

| Johann Großschädl, Roberto M. Avanzi, Erkay Savaş,<br>Stefan Tillich                                             | 75  |

| Short Memory Scalar Multiplication on Koblitz Curves  Katsuyuki Okeya, Tsuyoshi Takagi, Camille Vuillaume        | 91  |

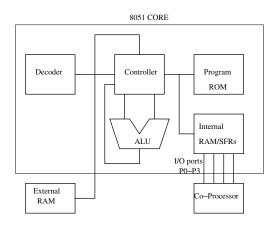

| Hardware/Software Co-design for Hyperelliptic Curve Cryptography (HECC) on the 8051 $\mu P$                      |     |

| Lejla Batina, David Hwang, Alireza Hodjat, Bart Preneel, Ingrid Verbauwhede                                      | 106 |

| Special Purpose Hardware                                                                                         |     |

| SHARK: A Realizable Special Hardware Sieving Device for Factoring                                                |     |

| 1024-Bit Integers  Jens Franke, Thorsten Kleinjung, Christof Paar, Jan Pelzl,  Christine Priplata, Colin Stahlke | 119 |

| Scalable Hardware for Sparse Systems of Linear Equations, with Applications to Integer Factorization  Willi Geiselmann, Adi Shamir, Rainer Steinwandt, Eran Tromer | 131 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Design of Testable Random Bit Generators  Marco Bucci, Raimondo Luzzi                                                                                              |     |

| Hardware Attacks and Countermeasures I                                                                                                                             |     |

| Successfully Attacking Masked AES Hardware Implementations Stefan Mangard, Norbert Pramstaller, Elisabeth Oswald                                                   | 157 |

| Masked Dual-Rail Pre-charge Logic: DPA-Resistance Without Routing Constraints                                                                                      |     |

| Thomas Popp, Stefan Mangard                                                                                                                                        | 172 |

| Masking at Gate Level in the Presence of Glitches Wieland Fischer, Berndt M. Gammel                                                                                | 187 |

| Arithmetic for Cryptography                                                                                                                                        |     |

| Bipartite Modular Multiplication  Marcelo E. Kaihara, Naofumi Takagi                                                                                               | 201 |

| Fast Truncated Multiplication for Cryptographic Applications $ \textit{Laszlo Hars} \$                                                                             | 211 |

| Using an RSA Accelerator for Modular Inversion  Martin Seysen                                                                                                      | 226 |

| Comparison of Bit and Word Level Algorithms for Evaluating<br>Unstructured Functions over Finite Rings                                                             |     |

| B. Sunar, D. Cyganski                                                                                                                                              | 237 |

| Side Channel II (EM)                                                                                                                                               |     |

| EM Analysis of Rijndael and ECC on a Wireless Java-Based PDA Catherine H. Gebotys, Simon Ho, C.C. Tiu                                                              | 250 |

| Security Limits for Compromising Emanations  Markus G. Kuhn                                                                                                        | 265 |

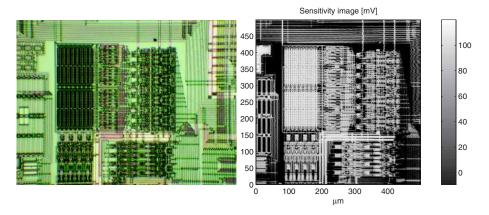

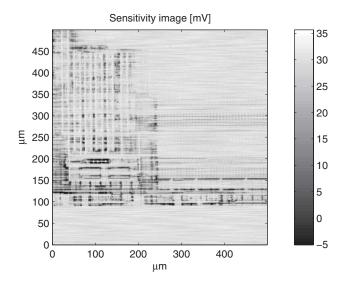

| Security Evaluation Against Electromagnetic Analysis at Design Time Huiyun Li, A. Theodore Markettos, Simon Moore                                                  | 280 |

| Side Channel III                                                                                                                                                                        |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| On Second-Order Differential Power Analysis  Marc Joye, Pascal Paillier, Berry Schoenmakers                                                                                             | 293 |

| Improved Higher-Order Side-Channel Attacks with FPGA Experiments  Eric Peeters, François-Xavier Standaert, Nicolas Donckers,  Jean-Jacques Quisquater                                   | 309 |

| Trusted Computing                                                                                                                                                                       |     |

| Secure Data Management in Trusted Computing  Ulrich Kühn, Klaus Kursawe, Stefan Lucks, Ahmad-Reza Sadeghi,  Christian Stüble                                                            | 324 |

| Hardware Attacks and Countermeasures II                                                                                                                                                 |     |

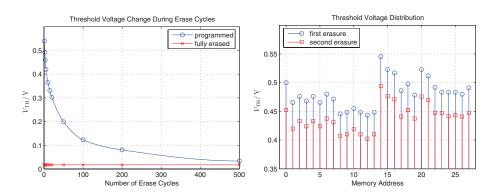

| Data Remanence in Flash Memory Devices  Sergei Skorobogatov                                                                                                                             | 339 |

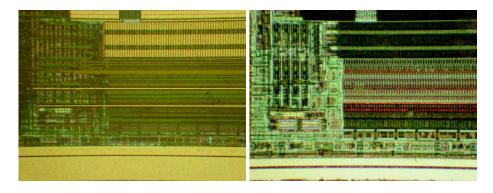

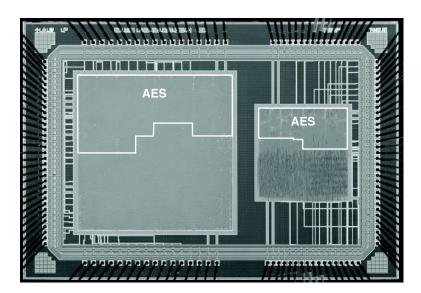

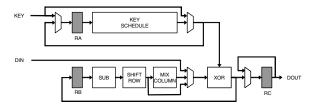

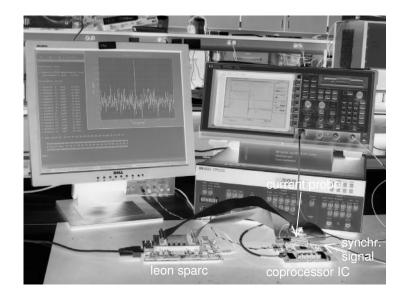

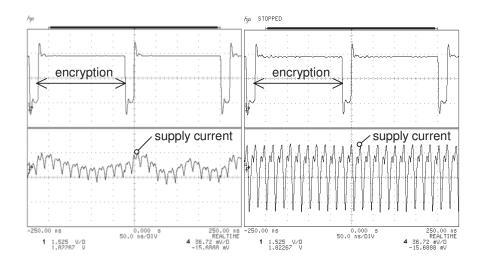

| Prototype IC with WDDL and Differential Routing – DPA Resistance Assessment  Kris Tiri, David Hwang, Alireza Hodjat, Bo-Cheng Lai, Shenglin Yang, Patrick Schaumont, Ingrid Verbauwhede | 354 |

| Hardware Attacks and Countermeasures III                                                                                                                                                |     |

| DPA Leakage Models for CMOS Logic Circuits  Daisuke Suzuki, Minoru Saeki, Tetsuya Ichikawa                                                                                              | 366 |

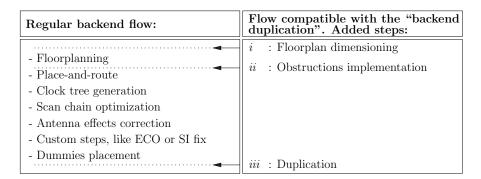

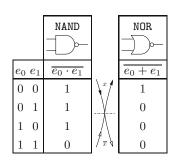

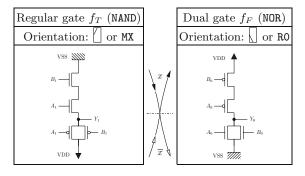

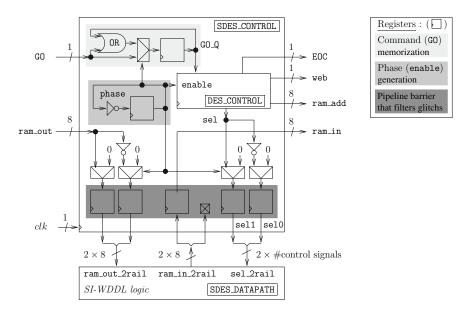

| The "Backend Duplication" Method  Sylvain Guilley, Philippe Hoogvorst, Yves Mathieu,  Renaud Pacalet                                                                                    | 383 |

| Efficient Hardware I                                                                                                                                                                    |     |

| Hardware Acceleration of the Tate Pairing in Characteristic Three  P. Grabher, D. Page                                                                                                  | 398 |

| Efficient Hardware for the Tate Pairing Calculation in Characteristic Three                                                                                                             |     |

| T. Kerins, W.P. Marnane, E.M. Popovici, P.S.L.M. Barreto                                                                                                                                | 412 |

## XIV Table of Contents

# Efficient Hardware II

| AES on FPGA from the Fastest to the Smallest  Tim Good, Mohammed Benaissa | 427 |

|---------------------------------------------------------------------------|-----|

| A Very Compact S-Box for AES  D. Canright                                 | 441 |

| Author Index                                                              | 457 |

# Resistance of Randomized Projective Coordinates Against Power Analysis

William Dupuy and Sébastien Kunz-Jacques

DCSSI Crypto Lab, 51, bd de Latour-Maubourg, 75700 PARIS 07 SP william.dupuy@laposte.net kunzjacq@yahoo.fr

**Abstract.** Embedded devices implementing cryptographic services are the result of a trade-off between cost, performance and security. Aside from flaws in the protocols and the algorithms used, one of the most serious threats against secret data stored in such devices is Side Channel Analysis.

Implementing Public Key Cryptography in low-profile devices such as smart cards is particularly challenging given the computational complexity of the operations involved. In the area of elliptic curve cryptography, some choices of curves and coefficient fields are known to speed up computations, like scalar multiplication. From a theoretical standpoint, the use of optimized structures does not seem to weaken the cryptosystems which use them. Therefore several standardization bodies, such as the NIST, recommend such choices of parameters. However, the study of their impact on practical security of implementations may have been underestimated.

In this paper, we present a new chosen-ciphertext Side-Channel Attack on scalar multiplication that applies when optimized parameters, like NIST curves, are used together with some classical anti-SPA and anti-DPA techniques. For a typical exponent size, the attack allows to recover a secret exponent by performing only a few hundred adaptive power measurements.

#### 1 Introduction

The use of elliptic curves for cryptographic purposes was proposed by Miller [10] in 1985 and Koblitz [8] in 1987. Since then, it became an essential part of public key cryptography. In particular, many cryptosystems rely on the intractability of the discrete logarithm problem (DLP) on elliptic curves. The main advantage of this problem is that it is believed to be harder to solve than other number-theoretic problems. As a consequence, for a similar security level, it is possible to use smaller objects than with integer factorization for example. This property is especially attractive for embedded systems, where storage requirements and computation times are critical.

Cryptosystems relying on DLP on elliptic curves use the scalar multiplication operation in some large elliptic curve group (G, +)

$$P \in G \to kP \tag{1}$$

where k is a secret data. Because of DLP hardness, it is believed to be infeasible to compute k from the knowledge of one or several pairs (P, kP).

In a situation where no reasonable attack on a cryptographic algorithm is known, Kocher first observed in 1996 [9] that the measurement of the algorithm computation time could still reveal secret information. This paved the way to Side Channel Attacks that take advantage of the measurement of physical signals emitted by a cryptographic device during a computation to gain access to secret data.

Since then, several examples of Side Channel Attacks led to various countermeasures being developed. Concerning scalar multiplication in EC groups, the use of scalar multiplication algorithms with a regular computation flow like double-and-add always or Montgomery Ladder is an answer to Simple Power Analysis (SPA), while randomized projective coordinates, first proposed by [4], are used to counter Differential Power Analysis (DPA).

In this paper, we present a new side-channel attack against scalar multiplication implementing these countermeasures, when the EC group used is chosen among the NIST [12], ANSI [1] or SEC [13] recommended curves. It is a Goubin-style attack [6] that uses distinguished points whose presence can be detected along the computation by an observation of power traces despite the randomization countermeasure. It leverages the particular shape of the underlying coefficient fields.

The paper is organized as follows. We first briefly review some facts about elliptic curves in section 2. Then section 3 presents some classical Side Channel Attacks and common countermeasures to prevent them. Finally, sections 4 and 5 present the details of our attack.

## 2 Elliptic Curves

#### 2.1 Elliptic Curve Equation

Let  $\mathbb{K}$  be a finite field of characteristic p. Over this field, we set the equation (E)

$$y^2 + a_1 xy = x^3 + a_2 x^2 + a_4 x + a_6$$

The elliptic curve (C) associated to (E) is the set of all points of  $\mathbb{K}^2$  satisfying (E), together with a particular point  $\mathcal{O}$  called *point at infinity*.  $\mathbb{K}$  is the *coefficient field* of the curve.

Up to an affine change of variables, if p=2, we can set  $a_1=1$  and  $a_4=0$ . The equation can then be rewritten  $y^2+xy=x^3+a_2x^2+a_6$ . If  $p\geq 3$ , we can set  $a_1=a_2=0$  and then (E) becomes  $y^2=x^3+a_4x+a_6$ .

Together with an addition law, this set forms a commutative group. We do not describe the group law here since it does not play any role in the attack we present.

#### 2.2 Affine and Projective Representation

A point on a curve of equation (E) is a solution of (E). Therefore the simplest representation of a point on a curve of equation (E) is the corresponding solution of (E) in  $\mathbb{K}^2$ . This is the *affine* representation.

Nevertheless, other representations can be preferred. We are mainly interested in *projective coordinates*. Given P=(x,y) in affine coordinates, its representation in projective coordinates is P=(xZ,yZ,Z) for any  $Z\in\mathbb{K}^*$ . If a finite solution of (E) is represented by  $(\alpha,\beta,\gamma)$ , then  $\gamma\neq 0$ . The point at infinity  $\mathcal O$  is represented by  $(0,\beta,0)$  for any  $\beta\neq 0$ .

The projective representation is not unique. In fact, for some finite solution (x,y) of (E) with  $x \neq 0$  and  $y \neq 0$ , any of the three projective coordinates can take an arbitrary value in  $\mathbb{K}^*$ . This observation is the basis of the randomized projective coordinates countermeasure, which we will describe in section 3.2. Projective representation is also used to increase the efficiency of point addition computations since for example, it allows to compute the group law without having to perform modular inversion in the coefficient field.

#### 2.3 Recommended Coefficient Fields for NIST Elliptic Curves

Curves recommended by standardization bodies such as NIST, ANSI, or SEC are usually defined over  $\mathbb{F}_p$ , or  $\mathbb{F}_2[x]/(P)$  where P a primitive polynomial. We focus on NIST recommended curves from now on. Other standardized curves present similar properties as the ones of the NIST.

Curves Defined on Binary Fields. The coefficient field is here of the form  $\mathbb{F}_2[x]/(P)$ . The primitive polynomials standardized by the NIST are:

$$P_{233}(x) = x^{233} + x^{74} + 1$$

$$P_{283}(x) = x^{283} + x^{12} + x^7 + x^5 + 1$$

$$P_{409}(x) = x^{409} + x^{87} + 1$$

$$P_{571}(x) = x^{571} + x^{10} + x^5 + x^2 + 1$$

We can notice that these polynomials are very sparse. This has to do with hardware efficiency.

Curves Defined on Prime Order Fields. For these curves, the coefficient field is  $\mathbb{F}_p$ , with p among

$$p_{192} = 2^{192} - 2^{64} - 1$$

$$p_{224} = 2^{224} - 2^{96} + 1$$

$$p_{256} = 2^{256} - 2^{224} + 2^{192} + 2^{96} - 1$$

$$p_{384} = 2^{384} - 2^{128} - 2^{96} + 2^{32} - 1$$

$$p_{521} = 2^{521} - 1$$

As in the binary case, the sparse form of these primes simplifies and speeds up operations in the coefficient field.

#### 2.4 Scalar Multiplication

As already mentioned, cryptosystems relying on discrete logarithm on elliptic curves make a consistent use of *scalar multiplication*. Given a public point P on the elliptic curve, and a secret scalar k, this operation consists in computing kP.

Let us write  $k = \sum_{i=0}^{n-1} k_i 2^i$ . The most basic algorithm that computes kP given P and a "black-box" implementation of the group law is the following:

```

[double-and-add from MSB to LSB]

INPUT: P in C

R=0

for i from n-1 to 0

R <- 2R

if k_i=1

R <- R+P

end for;

RETURN R</pre>

```

#### 3 Side Channel Attack and Common Countermeasures

#### 3.1 Classes of Attacks

**SPA:** Simple Power Analysis applies when the sequence of operations performed during some computation depends on a secret value. When the operations used are sufficiently complex, they can be easily detected by physical measures and the sequence of operations performed can be retrieved.

For instance, in a *double-and-add* algorithm, an addition is performed only if the corresponding bit of k is set to 1. Assuming that doubling and adding have noticeably different power consumption signatures, one observation of a power consumption curve can be enough to extract the secret exponent value.

**DPA:** Differential Power Analysis was introduced by [3] on DES implementations, but it applies to public-key cryptography as well.

For DPA to work, some intermediate value v manipulated by a cryptographic device must depend on known input and output values and on a few secret bits. The power consumption of some operation manipulating v is measured for several input values. To each value k of the secret bits involved corresponds a partition of the input and output messages into subsets leading to the same value for v. A guess for k can be checked as follows: if the value of k is correct, averaging the power consumption inside these subsets should yield noticeably different results among subsets. If it is wrong, results should be roughly identical no matter the subset chosen.

Goubin-Style Attacks. L. Goubin [6] first noticed that some properties of intermediate values may be invariant under randomization. For example, if a coordinate of some projective point representation is zero, it remains equal to zero whatever the randomization applied. If such a remarkable property can be detected, an attack can be built as follows: input values are chosen so that a remarkable value appears during the computation only if some hypothesis about a secret is correct. The measure then allows the attacker to test his hypothesis.

The attack we present follows this framework.

#### 3.2 Countermeasures

Many countermeasures have been developed to make the attacks presented in section 3.1 impractical. Most widely used ones are presented here.

Regularization of the Instructions Flow. For an algorithm to be protected against SPA, its instruction flow must not depend on secret values. *Double-and-add always*, or *Montgomery ladder* [11] are examples of such algorithms:

```

[Double-and-add always from MSB to LSB]

INPUT: P in C

R[0]=0

for i from n-1 to 0

R[0] \leftarrow 2R[0]

R[1] \leftarrow R[0] + P

R[0] \leftarrow R[k_i]

end for;

RETURN R[0]

[Montgomery ladder]

INPUT: P in C

R[0]=0;R[1]=P

for i from n-1 to 0

R[1-k_i] < - R[k_i] + R[1-k_i]

R[k_i] \leftarrow 2R[k_i]

end for;

RETURN R[0]

```

Randomization of Data Representation. is targeted at DPA. If the representation of temporary values is randomized, an intermediate value does not depend only on inputs and key bits, but also on some random data out of control of the attacker. Consequently, aggregating measures is no longer possible.

In the case of scalar multiplication, expressing a point in randomized projective (or Jacobian) form, as suggested by Coron [4], is a common instantiation of this countermeasure.

Randomization of the computation flow In order to prevent Goubin-style attacks, randomness can be introduced in the sequence of operations performed. Here are two examples of techniques applied to the scalar multiplication  $P \to kP$ :

- **Point blinding** The hardware computes k(P + R) and kR, for some random point R, separately [4] or together using a trick due to Shamir [7].

- Random exponent If q is the order of the underlying group, then qP = 0. Therefore if (k + rq)P is computed instead of kP for some random value r, the final result is unchanged, but the binary representation of the secret key is scrambled by the addition of rq all along the computation.

## 4 The Attack: Theory

#### 4.1 Assumptions on the Target Device

We aim at retrieving the *n*-bit secret scalar k stored in a cryptographic device performing scalar multiplication  $P \to kP$  for any point P of our choice, on an elliptic curve whose coefficient field is defined by a sparse polynomial for the binary field case or a "sparse" prime for the prime field case (see 2.3).

An element e in the coefficient field can always be written  $e = \sum_{i=0}^{n-1} e_i u^i$  with

u=2 if  $\mathbb{K}=\mathbb{F}_p$ , and u=x if  $\mathbb{K}=\mathbb{F}_{2^n}=\mathbb{F}_2[x]$ . Since we will observe Hamming weights during the attack, we assume that our target crypto device represents e in the standard way by the binary string  $\{e_i\}$ .

The secret scalar, on the other hand, is an object of  $\mathbb{Z}/q\mathbb{Z}$  where q is the number of elements of the chosen elliptic curve group. We will write

$$k = \sum_{i=0}^{n-1} k_i 2^i$$

The attack we propose applies to implementations having the following properties:

- Points are represented with randomized projective coordinates.

- No randomization of the computation flow is performed.

We focus on double-and-add always from the MSB to the LSB or on the Montgomery ladder. However, the particular choice of the scalar multiplication algorithm used is irrelevant, and we target more generally algorithms that perform one computation step per exponent bit. We suppose that in step j the point  $K_jP$  is manipulated, with

$$K_j = \sum_{i=n-1-j}^{n-1} k_i 2^{i-(n-1-j)}$$

On the measurement side, we assume we have access to the Hamming weights of the values manipulated, up to some noise.

#### 4.2 Overview of the Attack

Suppose that some special point  $P_0$  can be distinguished from a random point, for example by power analysis. Since we assumed in section 4.1 that on input P and during step j, the multiplication algorithm manipulates

$$K_j.P = \left(\sum_{i=n-1-j}^{n-1} k_i 2^{i-(n-1-j)}\right) P$$

asking for the computation of  $k.(1/K_jP_0)$  makes  $P_0$  appear at the j-th step of computation. Because  $K_j = 2K_{j-1} + k_{n-1-j}$ , assuming  $K_{j-1}$  is known, the value of the next unknown bit  $k_{n-1-j}$  can be recovered as follows:

Assume that  $k_{n-1-j}=0$  and that consequently  $K_j=2K_{j-1}$ . Observe the computation of  $k(1/K_j)P_0$ . If  $P_0$  is detected at step j, the hypothesis on bit  $k_{n-1-j}$  was correct. Otherwise,  $k_{n-1-j}=1$  and  $K_j=2K_{j-1}+1$ .

The above applies for j=0 as well with  $K_{-1}=0$ .

For each bit, several computations might be performed to improve the reliability of the guess of  $k_{n-j}$ . Then, by iterating this algorithm, the whole secret k can be extracted.

#### 4.3 Using Hamming Weights to Build a Distinguishable Point

We choose a point of the form

$$P_0 = (u^{\lambda}, y)$$

in affine coordinates, with  $\lambda$  as small as possible. Its representation in projective form is  $P_0: (X=u^{\lambda}Z, Y=yZ, Z)$  for some random  $Z\in \mathbb{K}^*$ .

For each value of  $\lambda$  we can expect that there is a point with abscissa  $u^{\lambda}$  with probability 1/2: in  $\mathbb{F}_p$ , this is the case if and only if  $2^{3\lambda}+a2^{\lambda}+b$  is a square, while in  $\mathbb{F}_{2^n}$ , it depends on whether the polynomial  $p(y)=y^2+x^{\lambda}y+x^{3\lambda}+ax^{2\lambda}+b$  has roots. For all NIST curves,  $\lambda$  can be chosen  $\leq 5$ .

**Detecting the Distinguishable Point.** Because of the form of common coefficient fields such as NIST fields, we show in sections 4.4 and 4.5 that for a random Z,  $X = u^{\lambda}Z$  is close to Z rotated by  $\lambda$  bits on the left  $(Z <<< \lambda)$ , therefore

$$U = \mathsf{Ham}(X) - \mathsf{Ham}(Z)$$

is small. At the opposite, for a random point where coordinates are uncorrelated, U has mean 0 and variance V(U) = 2(n/4) = n/2. Therefore,

We measure U to discriminate  $P_0$  from a random point.

As usual, increasing the number of experiments decreases the error probability; several scalar multiplications lead to as many observations of U as necessary. Statistical tests can then be performed as described in section 5.1 to make a decision according to the observations.

Now, let us estimate the Hamming distance between  $u^{\lambda}Z$  and  $(Z <<< \lambda)$  on both fields types.

#### 4.4 Binary Fields

Let  $P(x) = 1 + x^n + \sum_{i=1}^I x^{m_i}$  with  $1 \le m_i < m_{i+1} < n$  be a primitive polynomial over  $\mathbb{Z}_2[X]$  of degree n. Let  $e = n - \deg(P(x) - x^n) = m_I$ . We assume that  $e > \lambda$ ; this is true for NIST curves which satisfy e > n/2. More generally, multiplication optimization in  $\mathbb{F}_{2^n} = \mathbb{F}_2[x]/(P)$  commands to choose e large.

Let  $Z \in \mathbb{F}_{2^n}$ . Remember that elements of  $\mathbb{F}_{2^n}$  are represented in the usual polynomial base. For  $\lambda < e$ , set  $Z = Z_1 + x^{n-\lambda}Z_2$  with  $\deg(Z_1) < n - \lambda$  and  $\deg(Z_2) < \lambda : (Z <<< \lambda) = x^{\lambda}Z_1 + Z_2$ .

$x^{\lambda}Z$  and  $(Z <<< \lambda)$  mod P are related by:

$$x^{\lambda}Z \equiv x^{\lambda}Z_1 \oplus x^nZ_2$$

$$\equiv x^{\lambda}Z_1 \oplus (x^n - P)Z_2$$

$$\equiv (Z <<< \lambda) \oplus Z_2 \oplus (x^n - P)Z_2$$

$$\equiv (Z <<< \lambda) \oplus \sum_{i=1}^{I} x^{m_i} Z_2$$

Since  $\lambda < e$ , the above result is the reduced expression of the difference mod P. Each term  $x^{m_i}Z_2$  is a  $\lambda$ -bit pattern that can affect at most a  $\lambda$ -bit window of the difference. Therefore at most  $I\lambda$  bits differ from Z and  $x^{\lambda}Q$ .

Under the assumption that the  $\lambda$ -bit windows do not overlap, the exact computation of the probability law of  $\mathsf{Ham}(x^\lambda Q) - \mathsf{Ham}(Q)$  can be carried out; this is useful to improve the attack (see section 5.1, Neyman-Pearson). The computation is performed in appendix A.1. The non-overlapping assumption is satisfied for the NIST curves  $P_{233}$  and  $P_{409}$ .

#### 4.5 Prime Fields

We work here in  $\mathbb{F}_p$  with p is prime. This case is more complex than the binary case because of the carry propagations that occur while adding values mod p.

Let e be the the greatest integer such that  $2^n - 1 - p < 2^{n-e}$ . For all NIST curves,  $e \ge 32$ . Distinguished points for curves on prime fields satisfy  $\lambda \le 3$ : thus we always have  $e - \lambda \ge 29$ .

Let

$$Z \in \mathbb{F}_p$$

,  $Z = Z_1 + 2^{n-\lambda}Z_2$ , with  $Z_1 < 2^{n-\lambda}$  and  $Z_2 < 2^{\lambda}$ .  $(Z <<< \lambda) = 2^{\lambda}Z_1 + Z_2$  and

$$2^{\lambda}Z \equiv 2^{\lambda}Z_1 + 2^nZ_2[p]$$

$$\equiv 2^{\lambda}Z_1 + (2^n - p)Z_2[p]$$

$$\equiv (Z <<< \lambda) + \Delta[p] \quad \text{with } \Delta = (2^n - 1 - p)Z_2$$

Since  $Z_2 < 2^{\lambda}$  and  $2^n - 1 - p \le 2^{n-e}$ ,  $\Delta < 2^{n-(e-\lambda)}$ . Since  $p \ge 2^n - 2^{n-e}$ , with probability around  $1 - 2^{e-\lambda} \ge 1 - 2^{-29}$ ,  $(Z <<< \lambda) + \Delta$ , viewed as an integer, is reduced mod p (i.e. it lies in the interval [0, p-1]). We can thus forget reduction mod p and study the effect of adding  $\Delta$  to  $(Z <<< \lambda)$  in  $\mathbb{Z}$ .

Sparse primes like NIST primes satisfy relations of the form  $2^n-1-p=\sum_{i=1}^I \varepsilon_i \, 2^{m_i}$ , with I small and  $\varepsilon_i=\pm 1$  (see section 2.3; in the NIST case,  $I\leq 3$ ). Therefore  $\Delta=\sum_{i=1}^I \varepsilon_i \, 2^{m_i} \, Z_2$ .  $\Delta$  is composed of I  $\lambda$ -bit blocks; we now assume as in the binary case that these blocks do not overlap, and this hypothesis is fulfilled for all NIST curves mod p.

On average, carries beyond  $\lambda$ -bit blocks of multiples of  $Z_2$  ("block carries") do not change  $U = \operatorname{Ham}(Z <<< \lambda) - \operatorname{Ham}(2^{\lambda}Z)$ , and have a small influence on V(U) as shown in appendix A.2. Since inside each block the Hamming weight is not changed on average,  $\mathsf{E}(U) = 0$  as in the binary case. Excluding the block carries, at most  $I\lambda$  bits differ between  $2^{\lambda}Z$  and Z.

#### 5 The Attack: Practice

#### 5.1 Statistical Tests

During the course of the attack, we target some specific bit  $k_{n-j}$  manipulated during step j+1. We compute m times  $k.(1/(2K_j)P_0)$  and collect m measures  $U_i$ ,  $1 \leq i \leq m$ , of U. We must then choose a guess for  $k_{n-j}$  depending on  $S = (U_1, \ldots, U_m)$ . Let  $\mathcal{D}_h$  be the law of U if  $k_{n-j} = h$ ,  $\mathsf{P}_{\mathcal{D}_0}(U = k) = p_{k,0}$  and  $\mathsf{P}_{\mathcal{D}_1}(U = k) = p_{k,1}$ .

**Neyman-Pearson Test.** It is well known from the Neyman-Pearson lemma that the test that has the smallest error probability if both hypothesis on  $k_{n-j}$  are equally likely, consists in computing the probability of the sample S observed according to both hypotheses, and to select the hypothesis  $k_{n-j} = h$  for which the probability of the sample is the highest; this is the hypothesis that explains best the observed value. Knowing the  $p_{k,h}$ , one can compute the probability of S under hypothesis h through

$$\mathsf{P}_{\mathcal{D}_h}(S) = \mathsf{P}_h = p_{U_1,h} p_{U_2,h} \dots p_{U_m,h} \tag{2}$$

**Test Based on a Variance Estimator.** While the Neyman-Pearson test on S is optimal, it requires the exact knowledge of  $\mathcal{D}_0$  and  $\mathcal{D}_1$ . A slightly less efficient, but simpler test consists in estimating the variance of S. If  $k_{n-j} = 0$ ,  $V(U) = V_0 = (I\lambda)/2$  (binary case) or  $(I(\lambda + 1))/2$  (prime case), whereas if  $k_{n-j} = 1$ ,  $V(U) = V_1 = n/2$ .

After m experiments, V(U) is estimated by  $\overline{V} = \frac{1}{m} \sum_{i=1}^{m} U_i^2$ . The probability  $\mathsf{P}_h$  that  $\overline{V}$  takes some specific value under  $\mathcal{D}_h$  is then computed by approximating both laws  $\mathcal{D}_0$  and  $\mathcal{D}_1$  by normal laws<sup>1</sup>: the law of  $\overline{V}$  under  $\mathcal{D}_h$  is approximated by  $V_h/m$  times a  $\chi_2$  with m degrees of freedom. The Neyman-Pearson decision rule is then used on  $\overline{V}$ :  $k_{n-j} = 0$  is decided if and only if  $\mathsf{P}_0 > \mathsf{P}_1$ .

**Necessary Number of Experiments.** The error probability of the Neyman-Pearson decision rule on some function f of the observation S for one experiment depends on the statistical distance between  $f(\mathcal{D}_0)$  and  $f(\mathcal{D}_1)$

$$\sum_{k} |\mathsf{P}_{\mathcal{D}_0}(f(S) = k) - \mathsf{P}_{\mathcal{D}_1}(f(S) = k)|$$

and similarly, on several experiments, the distance between  $f(\mathcal{D}_0) \times \dots f(\mathcal{D}_0)$  and  $f(\mathcal{D}_1) \times \dots \times f(\mathcal{D}_1)$  could be computed. However, this is not practical. Some approximations exist, like the Kullback-Leibler distance, or the Square Euclidean Imbalance (see [2] or [5]). Very roughly, they state that for a constant error rate the number of experiments depends on the distributions like  $\left(\sum_k [\mathsf{P}_{\mathcal{D}_0}(f(S) = k) - \mathsf{P}_{\mathcal{D}_1}(f(S) = k)]^2\right)^{-1}$ . Practically, we prefer adaptive strategies that estimate on the fly the error

Practically, we prefer adaptive strategies that estimate on the fly the error probability.

**Adaptive Strategies.** If m measures are performed, resulting in some observation S of probability  $P_h$  under  $\mathcal{D}_h$ , the probability that hypothesis h actually holds is

$$P(h = 0|S) = \frac{P_0}{P_0 + P_1}$$

and  $P(h = 1|S) = \frac{P_1}{P_0 + P_1}$

During a series of m experiments, m being a fixed value, the probability ratio  $P(h=0|S)/P(h=1|S) = P_0/P_1$  indicates the confidence in the decision made. In the experiments we perform, some threshold  $\delta > 1$  is set. We perform more experiments as long as  $1/\delta < P_0/P_1 < \delta$ . If  $P_0 > \delta P_1$  we decide h=0, and if  $P_1 > \delta P_0$  we decide h=1. Since the number of experiments is computed adaptively, experiments are no longer independent and for example (2) is not strictly true anymore. However we assume that the confidence estimation  $P_0/P_1$  is still meaningful.

Recovering the Whole Key. Even if the error probability for each bit guess is small, since we are dealing with large secret values (at least 192 bits), the probability that at least one error occurs during the attack is high. Additionally, after one error at step j, since next experiments rely on the value of  $K_j$ , subsequent tests will fail to detect  $P_0$  and with high probability, the next guessed bits will be equal to 1.

Of course, one way to overcome this problem is to have a very low error probability per bit. However, more subtle approaches can be devised: for example, if

<sup>&</sup>lt;sup>1</sup> this is justified by the central limit theorem for  $\mathcal{D}_1$ ; for  $\mathcal{D}_0$ , this can be considered as an heuristic hypothesis.

a long run of ones is guessed, one can attempt to restart from the computation step where the run begins.

#### 5.2 Experimental Results

We simulated a Montgomery Ladder using randomized projective coordinates on the various NIST curves. We used the most basic variance estimator, with no backtracking in case of long runs of ones. We looked for the number of measurements required to guess the whole secret scalar with a success probability of 90%. No noise was added to the measurements, unlike in a real setting.

The number of measurements that had to be performed in order to reach a confidence level of 90% does not grow linearly in the size of the scalar. In fact, it depends on  $I\lambda$ ; this is to be expected because of the expression of V(U) under the hypothesis  $k_{n-1-j} = 0$ .

Current results are summarized in table 1 below.

| Curve     | Total number of experiments | Experiments per bit | λ    | $I\lambda$ |

|-----------|-----------------------------|---------------------|------|------------|

| $p_{192}$ | 1117                        | 6                   | 2    | 2          |

| $p_{224}$ | 2347                        | 10                  | 6    | 6          |

| $p_{256}$ | 2729                        | 11                  | 4    | 12         |

| $p_{384}$ | 2519                        | 7                   | 1    | 3          |

| $p_{521}$ | 1305                        | 3                   | n.a. | 0          |

| $B_{233}$ | 482                         | 2                   | 1    | 1          |

| $B_{283}$ | 1854                        | 7                   | 5    | 15         |

| $B_{409}$ | 789                         | 2                   | 1    | 1          |

| $B_{571}$ | 2219                        | 4                   | 5    | 15         |

Table 1. Experiments Required for a 90% Confidence Level

#### 6 Conclusion

In this paper, we presented a new chosen-ciphertext Side-Channel Attack on elliptic curve scalar multiplication. It does not apply to any elliptic curve, but rather to curves whose coefficient fields are chosen to enable efficient implementations on resource-constrained hardware; unfortunately, this kind of hardware is precisely the target of choice for Side-Channel Attacks.

The attack is able to defeat some widely used countermeasures like anti-SPA scalar multiplication algorithms and projective coordinate randomization. It is stopped by more complex defenses like point blinding and scalar randomization; these countermeasures do not however come for free in hardware. The attack might also be prevented if the cryptanalyst cannot have full control over the scalar multiplication input.

Practically, basic simulations show that the attack is able to recover a secret scalar with a success rate of 90% on any NIST curve using no more than 11 power measurements per bit guessed, using a very simple statistical test. This

lead us to think that it is a practical threat that should be taken into account by implementors.

#### References

- 1. ANSI X9.62-1998. Public Key Cryptography for the Financial Services Industry: The Elliptic Curve Digital Signature Algorithm (ECDSA), 1998.

- 2. T. Baigneres, P. Junod, and S. Vaudenay. How Far Can We Go Beyond Linear Cryptanalysis? In *Advances in Cryptology ASIACRYPT' 04*, volume 3329 of *LNCS*, pages 432–450. Springer-Verlag, 2004.

- 3. C.Kocher, J.Jaffe, and B.Jun. Differential Power Analysis. In *Advances in Cryptology CRYPTO'99*, volume 1666 of *LNCS*, pages 388–397. Springer-Verlag, 1999.

- 4. J.-S. Coron. Resistance Against Differential Analysis for Elliptic Curve Cryptography. In *Advances in Cryptology CHES'99*, volume 1717 of *LNCS*, pages 292–302. Springer-Verlag, 1999.

- W. Feller. An Introduction To Probability Theory and Its Applications. Wiley Series In Probability And Mathematical Statistics. John Wiley & Sons, 1968.

- L. Goubin. A Refined Power-Analysis Attack on Elliptic Curve Cryptosystems. In Advances in Cryptology – PKC'03, volume 2567 of LNCS, pages 199–210. Springer-Verlag, 2003.

- 7. K. Itoh, T. Izu, and M. Takenaka. Efficient Countermeasures Against Power Analysis for Elliptic Curve Cryptosystems. In *CARDIS*, pages 99–114, 2004.

- N. Koblitz. Elliptic Curve Cryptosystems. In Mathematics of Computation, volume 48, pages 203–209. Springer-Verlag, 1987.

- 9. C. Kocher. Timing Attacks on Implementations of Diffie-Hellman, RSA, DSS, and Other Systems. In N. Koblitz, editor, *Advances in Cryptology CRYPTO'96*, volume 1109 of *LNCS*, pages 104–113. Springer-Verlag, 1996.

- V. Miller. Use of Elliptic Curve in Cryptography. In Advances in Cryptology CRYPTO' 85, volume 218 of LNCS, pages 417–426. Springer-Verlag, 1985.

- P. Montgomery. Speeding the Pollard and Elliptic Curves Methods of Factorization, volume 44. Math. Comp, 1985.

- 12. NIST. Recommended Elliptic Curves for Federal Government Use, 2000.

- Standards for Efficient Cryptography Group/ Certicom Research. SEC 2: Recommended Elliptic Curve Cryptography Domain Parameters, Version 1.0, 2000. http://www.secg.org.

#### A Computation of the Probability Law of U

#### A.1 Binary Case

In that section, we compute the exact probability law of the Hamming weight difference between  $x^{\lambda}Z$  and  $Z <<< \lambda$ , under the assumption that the  $\lambda$ -bit windows do not overlap.

We use the same notations as in 4.4:  $\mathbb{F}_{2^n} = \mathbb{F}_2[X]/(P)$  and Z is a random uniform value in  $F_{2^n}$ . For some  $\lambda < n - k_I$ ,

$$U = \operatorname{Ham}(Z) - \operatorname{Ham}(x^{\lambda} Z)$$

is the random variable whose law we want to compute. We saw in section 4.4 that if  $Z = Z_1 + x^{n-\lambda}Z_2$  with  $\deg(Z_1) < n - \lambda$  and  $\deg(Z_2) < \lambda$ , then

$$x^{\lambda}Z \equiv (Z <<< \lambda) \oplus \sum_{i=1}^{I} x^{k_i}.Z_2$$

Set  $(Z <<< \lambda) = \sum_{i=0}^{n-1} z_i x^i$ . Then  $Z_2 = \sum_{j=0}^{\lambda-1} z_j x^j$ . Let  $U_j$  be the contribution of the j-th bit of  $Z_2$ ,  $z_j$ , to U. Under the non-overlapping condition,  $U = U_0 + \ldots + U_{\lambda-1}$  and

$$\begin{split} U_j &= \operatorname{Ham}(Z <<<\lambda) - \operatorname{Ham}\left((Z <<<\lambda) \oplus z_j \sum_{i=1}^I x^{k_i+j}\right) \\ &= z_j \sum_{i=1}^I (2z_{k_i+j} - 1) = z_j \left(2 \sum_{i=1}^I z_{k_i+j} - 2I\right) \end{split}$$

and for each  $i, j, z_j$  and  $z_{k_i+j}$  are independent because  $k_i \neq 0$ . If W is a binomial random variable  $\mathcal{B}(I, 1/2)$ ,

$$P(U_j = k) = \frac{1}{2} P(2W - I = k) \text{ if } k \neq 0$$

$$P(U_j = 0) = \frac{1}{2} + \frac{1}{2} P(2W = I)$$

In particular,  $\mathsf{E}(U_j)=0$ , and  $\mathsf{V}(U_j)=I/2$ . Now  $U_0,\ldots,U_{\lambda-1}$  depend on different bits of Z and are therefore independent: the law of U is simply the law of the sum of  $\lambda$  independent "copies" of  $U_0$ , for example. In order to implement a Neyman-Pearson test on outcomes of U, its law can therefore be derived by computing the  $\lambda$ -th convolution power of the law of  $U_0$ . In order to perform variance tests, we only need  $\mathsf{E}(U)=0$ , and  $\mathsf{V}(U)=I\lambda/2$ .

#### A.2 Large Prime Case

In the prime field case, we want to approximate the law of  $U = \mathsf{Ham}(Z) - \mathsf{Ham}(2^{\lambda}Z)$ , where  $0 \le Z < p$  is random and the Hamming weight is computed on reduced representations mod p.

In section 4.5, we proved that the law of U is very close to the law of

$$U' = \operatorname{Ham}(Z') - \operatorname{Ham}(Z' + \Delta)$$

with Z' a random value in  $[0, 2^n - 1]$ ,

$$\Delta = (2^n - p - 1)(Z' \mod 2^{\lambda}) = \sum_{i=1}^{I} \varepsilon_i \, 2^{m_i} \, (Z' \mod 2^{\lambda})$$

and  $\varepsilon_i = \pm 1$ . Set  $Z' \mod 2^{\lambda} = Z'_2$ .  $\lambda$  copies of  $Z'_2$  are added or subtracted at I different  $\lambda$ -bit windows in Z. For the prime numbers we consider,  $m_{i+1} - m_i \gg \lambda$  and we will therefore assume that these windows do not overlap, and even more, that no carry can propagate from one window to the other. We will handle separately bit differences occurring inside these windows and bit differences outside them, caused by carries overflowing the windows. The first category of bit differences will be enumerated by a random value  $U'_i$ , and the second one by  $U'_o$ :  $U' = U'_o + U'_i$ . We will assume that  $U'_i$  and  $U'_o$  are independent.

The contribution  $c_i$  of each  $\lambda$ -bit window to  $U_i'$  is a random binomial value satisfying  $c_i/2 - 1 \sim \mathcal{B}(\lambda, 1/2)$ , and these contributions are independent because they involve independent bits of Z' (and although they both involve  $Z_2'$ ). Therefore  $U_i'/2 - 1 \sim \mathcal{B}(I\lambda, 1/2)$ .

Let us focus on the contribution  $c_o$  of a term  $2^{m_i}Z'_2$  to  $U'_o$ , corresponding to a case  $\varepsilon_i = 1$ . With probability 1/2, no carry occurs and  $c_o = 0$ . If a carry occurs,  $c_o$  contributes to  $U'_o$  in the following way:

| Contribution | 1   | 0   | -1   | -i           |

|--------------|-----|-----|------|--------------|

| Probability  | 1/4 | 1/8 | 1/16 | $2^{-(i+2)}$ |

For example, in the second case of the above table, two bits 01 in Z' are changed by the carry into 10.

In fact,  $c_0 = b(1-Z)$  where b is a Bernoulli variable that is equal to one if and only if a carry occurs,  $P(Z=i) = 2^{-i+1}$  for  $i \geq 0$ , and b and Z are independent. With the help of this expression, one can check that  $E(c_o) = 0$  and  $V(c_o) = 1/2$ . We would have obtained the same result for  $\varepsilon_i = -1$ , although  $c_0$  would be changed into  $-c_0$ .

Finally, in the simplified model corresponding to the assumptions we made,  $\mathsf{E}(U) = 0$  and  $\mathsf{V}(U) = (I(\lambda+1))/2$ . Also note that the modeling above can be used to compute the probability law of U.

# Templates as Master Keys

Dakshi Agrawal<sup>1</sup>, Josyula R. Rao<sup>1</sup>, Pankaj Rohatgi<sup>1</sup>, and Kai Schramm<sup>2</sup>

IBM Watson Research Center, P.O. Box 704

Yorktown Heights, NY 10598, USA

{agrawal, jrrao, rohatgi}@us.ibm.com

Communication Security Group, Ruhr-Universität Bochum

Universitaetsstrasse 150, 44780 Bochum, Germany

schramm@crypto.ruhr-uni-bochum.de

Abstract. We introduce two new attacks: the *single-bit template attack* and the *template-enhanced DPA attack*. The single-bit template attack can be used very effectively to classify even *single* bits in a single side channel sample with a high probability of correctness. The template-enhanced DPA attack, combines traditional DPA with single-bit template attacks to show that if an adversary has access to a test card with even a slightly biased RNG, then he/she can break *protected* cryptographic implementations on a target card even if they have perfect RNGs. In support of our claim, we report results from experiments on breaking two implementations of DES and AES *protected by the masking countermeasure* running on smartcards of different manufacturers.

In light of these results, the threat of template attacks, generally viewed as intrinsically difficult to mount, needs to be reconsidered.

#### 1 Introduction

Several side channel cryptanalytic techniques, such as those based on measuring timing, power consumption and electromagnetic emanations have been used effectively to launch a wide range of attacks such as simple power analysis (SPA), differential power analysis (DPA), higher order DPA, template attacks and multichannel attacks [Koc96, KJJ99, AARR02, CRR02, ARR03] against a wide variety of cryptographic devices. While countermeasures, even provably secure ones, have been developed for some attacks such as DPA, the perceived difficulty (in terms of the work effort required by an adversary) of launching other attacks has led developers to discount their feasibility.

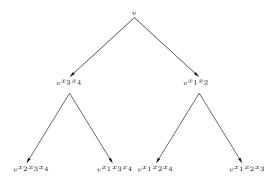

This is particularly true for template attacks. For instance, the very high successful classification results that can often be achieved with the analysis of a single side channel sample, make template attacks the ideal choice to attack ciphers, such as stream ciphers, which use ephemeral keys. However, until now all published works [CRR02, RO04] used template attacks to classify the state of a byte, e.g., a key byte in RC4. This makes the process of creating templates quite tedious since 256 templates need to be created for each byte. Further, templates for the full attack cannot be precomputed as the templates for a subsequent key

byte need to be created for each likely hypothesis for the earlier key bytes, i.e., the template building process can only be guided by partial attack results. In this paper, we show that this apparent difficulty is not intrinsic and present two new attack techniques to surmount it.

#### 1.1 Contributions

Our first contribution is the *single-bit template attack* technique. For a given bit, this attack uses DPA to build templates. It relies on our experimental observation that templates can be built from peaks observed in a DPA attack and these templates can predict the value of a single DPA-targeted bit in a single side channel sample with high probability. Thus, even though the specific computation yielding the single sample uses byte sized variables, the template can predict a single bit from those variables.

This technique immediately yields attacks where an adversary precomputes a large number of single-bit templates using several different DPA attacks on a test device and uses these precomputed templates and their classification probabilities to attack a single sample from an identical target device. These templates provide the best guess for each of the DPA-targeted bits and the template classification probabilities can be used to guide a weighted brute force search for the key. With enough precomputed templates, the entropy of the key is reduced substantially making the weighted brute force search practical. For example, in an experiment on a DES implementation, just attacking the 32-bits of S-box output in the first round, reduced the key entropy by over 16 bits. Clearly, by building templates, for DPA attacks carried on other variables in other rounds, the key entropy could be further reduced.

Reflecting further on the single-bit template attack, it should be evident, that knowledge of a single-bit template is comparable to having some partial knowledge about the key used in a card. Possession of several such single-bit templates is akin to having a master key that can be used to break any of a collection of cards from the same mask. This is true even for cards that are protected by DPA countermeasures such as secret sharing and random masking [GP99, CJR<sup>+</sup>99, AG01], if single-bit templates for the bits being processed in such cards can be built.

The second major contribution of this paper is to introduce template-enhanced DPA attacks which can be used to attack DPA protected cards under some assumptions. The problem with such cards is that single-bit templates (as described earlier) cannot be built, since in principle, the DPA protection renders DPA (the first step in building single-bit templates) infeasible. However, in practice, this is not a limitation, as there are multiple ways to get hold of a test card with a (slightly) biased RNG. For example, an adversary in collusion with the designers, testers and maintainers of card software may have hooks to add code to disable specific RNG registers on their own test cards while changes to deployed cards in the field may be much more tightly controlled and impossible for an adversary. Some production cards may fail the RNG tests at fabrication time and may be discarded only to be picked up by an adversary.

In our experience, we have sometimes encountered even production cards with slight RNG bias (to the tune of 3–4%). Therefore, if cards are not tested or tested to wide tolerance limits, then it is highly likely that several cards in the field may have slightly biased RNGs. As a last resort, an attacker could mount an intrusive attack to disable the RNG on his own test card.

Given a test card with a (slightly) biased RNG, an adversary can successfully perform multiple DPA attacks on the test card to build single-bit templates. The DPA peaks in these attacks would occur at locations where the masked value of the predicted variable bit (such as an S-box output bit) occur, since the masking is imperfect. Single-bit templates built using these DPA peaks would then be able to classify corresponding bits of the masked variables used in any card, including cards that have a perfect RNG. The template-enhanced DPA attack works by setting the DPA selector function to be the XOR of the standard DPA selector function (e.g., an S-box output bit for a key hypothesis) and the classification obtained by the single-bit templates (such as the masked S-box output bit). Depending on the effectiveness of the template classification, this DPA selector function will have high correlation with the mask bit being used. Thus for the right key hypothesis, this attack will show DPA peaks at locations where the random mask is being used.

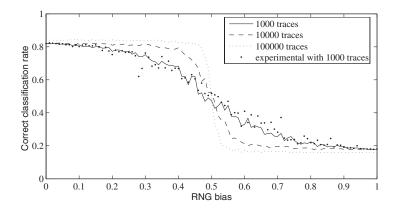

We demonstrate such a single-bit template attack for two DPA protected implementations: a protected DES implementation on a 6805 based smartcard and a protected AES implementation on an AVR architecture. We also report a surprising result that indicates that in practice, the bias of the RNG in the test card has little relevance to the effectiveness of the template-enhanced DPA attack. The RNG bias only affects the effort required to build single-bit templates. The classification error with single-bit templates built using a slightly biased RNG is not significantly worse than the classification error using templates built using a completely broken (fixed at 0) RNG.

The paper is organized as follows: In Section 2, we introduce single-bit template attacks. In Section 3, we introduce the template-enhanced DPA attacks and show how it can be uses to attack two smartcards of different architecture<sup>1</sup>, which run protected implementations of DES and AES.

#### 2 Single-Bit Template Attack

We extend earlier work on template attacks [CRR02, RO04] that focused on classifying a byte in a computation, e.g., a byte of key used in RC4, by showing how template attacks can be applied to classify single bits in a computation from a single side channel sample.

A template attack begins by selecting variables occurring in the computation for which templates would be built. Furthermore, it requires a selection of significant points for each of the selected variables that are included in the corresponding template. Having a good selection criterion for significant points

<sup>&</sup>lt;sup>1</sup> Smartcard A is an ST19 based on the 6805 architecture and smartcard B is an Atmel ATmega163 based on the AVR architecture.

is critical to the success of template attacks and this problem has been well studied: ideally, the significant points should have high variance with respect to the particular variable of interest. For example, Bohy et al. [BNSQ03] suggest Principal Component Analysis (PCA) while Rechberger et al. [RO04] suggest a simpler and computationally less expensive approach that resembles classical DPA. For the single-bit template attack, we let DPA attacks guide the selection of both the bits in the computation for which templates are built and significant points included in these templates. Templates are built for the bits for which a DPA attack is successful and the significant points included in a template are the points with the top N highest DPA-peaks.

We illustrate the attack by means of an example. Consider an unprotected implementation of DES on smartcard A. Consider the 32 s-box output bits of the DES computation in round one. For the unprotected DES implementation, one can easily perform DPA for each of the 32 output bits. Correspondingly, we built a pair of templates for each output bit corresponding to the bit being equal to 0 and 1 respectively. In order to build these templates, we performed a DPA of each output bit using the improved DPA metric described in [ARR03] which results in a higher signal-to-noise ratio (SNR) than the standard DPA. The improved metric is computed by using the following formula:

$$M_{H_i} = \frac{\left(\mu_{H_i} - \mu_{H_v}\right)^2}{\frac{\sigma_{H_v,0}^2}{N_0} + \frac{\sigma_{H_v,1}^2}{N_1}} - \ln\left(\frac{\frac{\sigma_{H_i,0}^2}{N_0} + \frac{\sigma_{H_i,1}^2}{N_0}}{\frac{\sigma_{H_v,0}^2}{N_0} + \frac{\sigma_{H_v,1}^2}{N_1}}\right)$$

(1)

where  $\mu_H$  is the difference of sample means of signals in the 0-bin and the 1-bin respectively for a hypothesis H. Similarly,  $\sigma_{H,0}^2$  and  $\sigma_{H,1}^2$  are the sample variances of the signals in the 0-bin and the 1-bin respectively for a hypothesis H.  $H_i$  denotes a hypothesis where a subkey is assumed to be i, and  $H_v$  is a special hypothesis (null hypothesis) where signals are partitioned in the 0-bin and the 1-bin randomly.

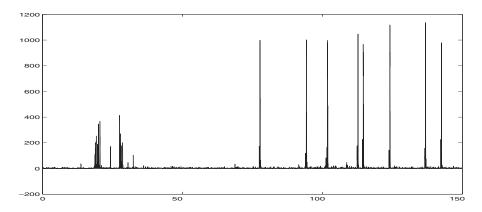

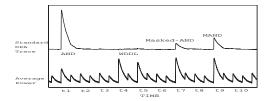

Figure 1 displays the improved metric of s-box 1, bit 0. The figure reveals several points in time that clearly correlate with the selected s-box output bit. In

Fig. 1. Improved DPA metric of s-box 1, bit 0 of the test device. Time in  $\mu$ s.

|                 | s-box |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                 | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     |

| bit 0           | 1.00  | 0.91  | 0.88  | 0.93  | 0.77  | 0.72  | 0.80  | 0.84  |

| bit 1           | 0.98  | 0.88  | 0.92  | 0.94  | 1.00  | 0.92  | 0.97  | 0.77  |

| bit 2           | 0.75  | 0.89  | 0.99  | 0.92  | 0.95  | 0.83  | 0.90  | 0.79  |

| bit 3           | 0.90  | 0.91  | 0.72  | 0.85  | 0.83  | 0.86  | 1.00  | 0.89  |

| entropy<br>loss | 2.57  | 2.10  | 2.13  | 2.30  | 2.28  | 1.50  | 2.61  | 1.35  |

Table 1. s-box output bit classification success rates and entropy loss

our experiments, we chose the 50 highest peaks from this DPA metric to select significant points and built a pair of templates for these points for each s-box output bit using a single set of 1400 side channel samples.

To estimate classification success rate, we classified the state of the 32 s-box output bits using a single set of another 100 random side channel samples measured from the same device. The classification success rates  $\eta_{S_ib_j}$  for the *i*-th s-box and j-th bit,  $1 \le i \le 8$  and  $0 \le j \le 3$ , together with the corresponding entropy loss are shown in Table 1. The classification success rates ranged from 0.72 to 1.00; in the worst case s-box 3, bit 3 and s-box 6, bit 0 were predicted correctly for only 72 of the 100 samples. From these results, the probability that the entire 32-bit output of all s-boxes is classified correctly is  $\prod_{i=1}^{8} \prod_{j=0}^{3} \eta_{S_ib_j} = 0.0154$  which although small is still 66-million times higher than a random guess.

These results can also be viewed in terms of entropy loss. For a particular bit, if the classification success rate is p, then its corresponding entropy loss is given by  $1 + (1 - p) \log_2(1 - p) + p \log_2(p)$ . To compute the entropy loss for multiple bits we can add the individual losses (this corresponds to the worst case where classification of different bits is independent). From this formula, we can see that 16.8-bits of entropy has been lost from the 48-bits of the DES key used in the first round (out of a maximum possible loss is 32-bits if the classification was perfect). The loss of entropy of the keyspace can be translated into reduced expected computational cost of a guided exhaustive search through the entire keyspace that examines more likely keys earlier than the less likely keys.

For DES implementations, the attack can be improved substantially. Templates can be built not just for round 1, s-box output bits but also for other bits such as the data bits fed to the second round. These templates will further narrow down the possibilities for the 48 key bits used in the first round. In addition, templates can be built for the corresponding DPA attacks on the last two rounds of DES (which utilize another 48-bit size subset of the key) and so on. Depending on the implementation, single-bit templates can also be built directly for the key bits that are likely to be highly effective since the same key bits show up in multiple locations in a round and across multiple rounds.

To summarize, single-bit template attacks are capable of classifying a single bit in a single side channel sample with high probability even though the influence of a single bit on the side channel signal is generally very little at

a particular instance of time, and is superimposed by several sources of noise including that from other adjacent bits. Cryptographic algorithms with high contamination properties [CRR02], such as DES, are ideally suited for single-bit classification. Multiple precomputed single-bit templates can lead to practical guided keyspace search algorithms using only a single sample from the target device. Moreover, single-bit attacks when combined with other attacks can result in much more devastating attacks as we show in the next section.

## 3 Attacking the Masking Countermeasure: Template-Enhanced DPA

The proposed attack consists of two steps: a profiling phase and a hypothesis testing phase. In the profiling phase, the adversary, who is in possession of a test card with a biased RNG, builds templates, and in the hypothesis testing phase, the adversary uses these prebuilt templates to mount a DPA-like attack on a target card which is identical to the test card, but has a perfect RNG.

#### 3.1 Profiling Phase

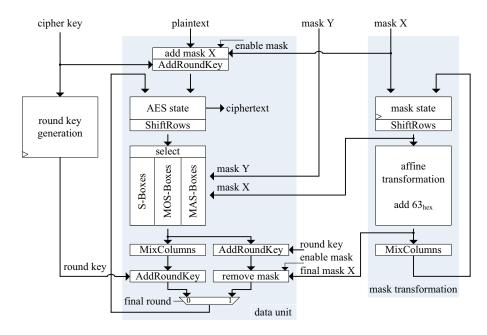

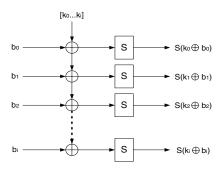

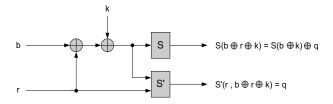

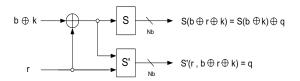

We assume that the adversary has a test card with a biased RNG that produces 0 bits with some biased probability  $\nu \neq 0.5$ , and that the adversary only faces masking countermeasures such as the duplication method [GP99]<sup>23</sup>. A masking countermeasure generally blinds all intermediate key-dependent variables with randomly generated masks. The original values of the intermediate variables can be recovered from their blinded values by applying the inverse mask. Nonlinear functions such as the s-boxes in DES and AES cannot be dealt with this way; they are typically handled by creating masked tables in RAM. While the unmasked s-box output  $s(x \oplus k)$  never occurs as a run-time variable during the execution of the algorithm, both the masked output  $s(x \oplus k) \oplus m$  and the mask m do occur and thus leak in the side channel sample.

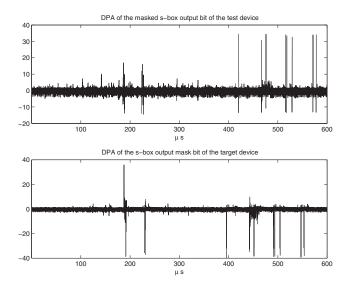

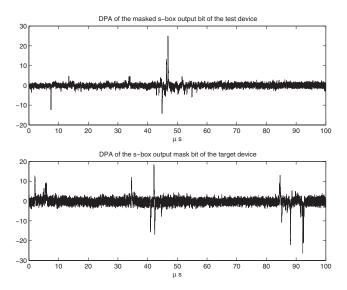

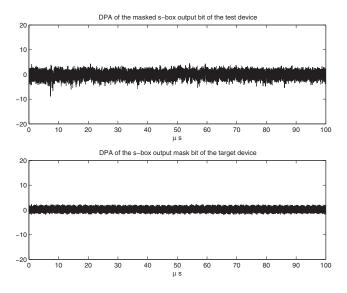

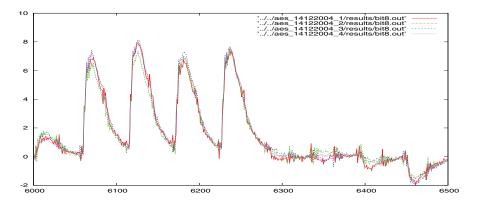

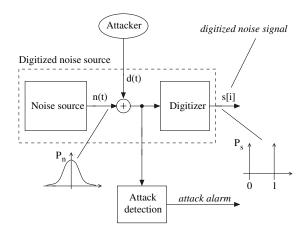

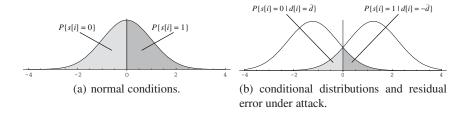

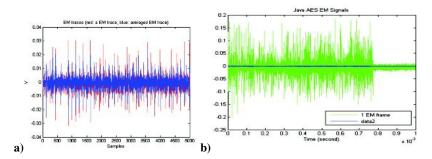

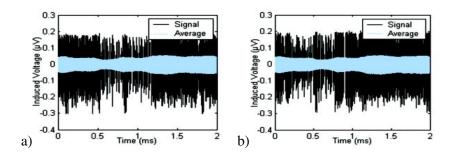

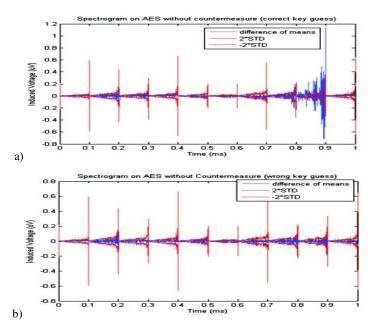

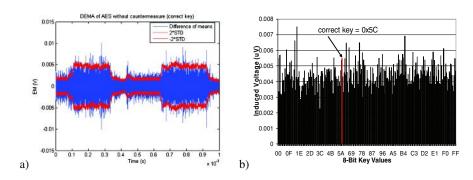

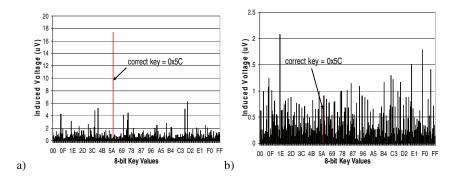

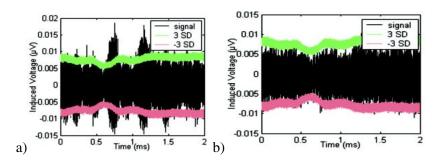

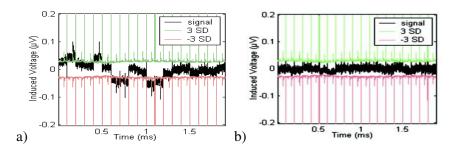

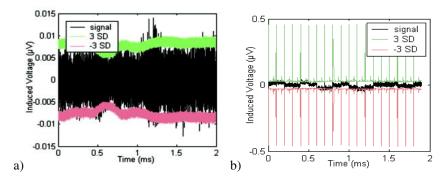

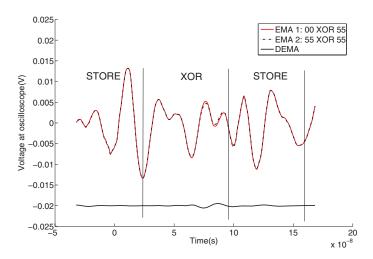

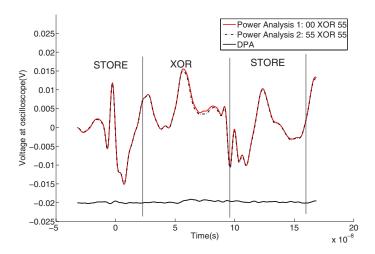

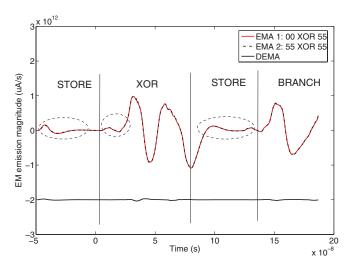

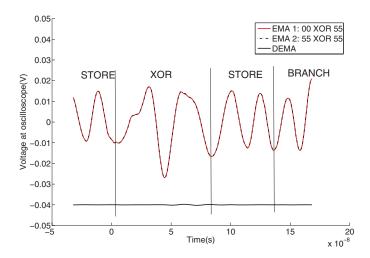

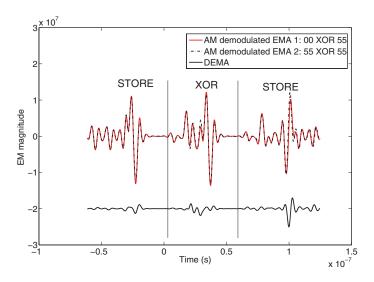

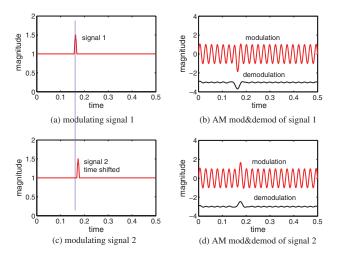

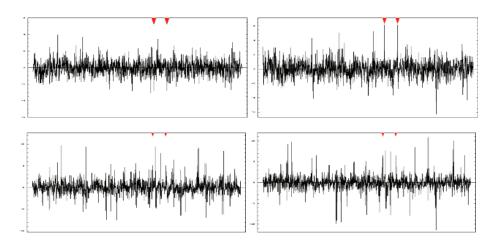

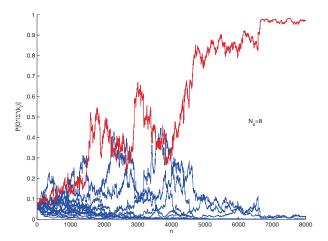

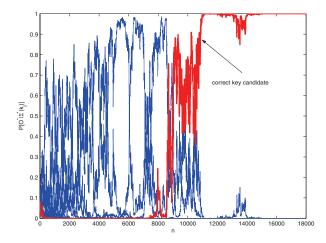

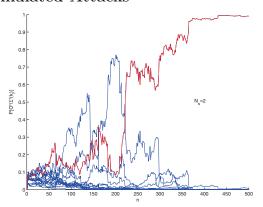

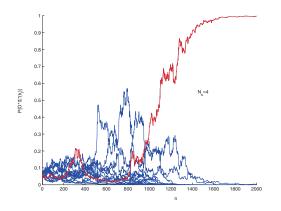

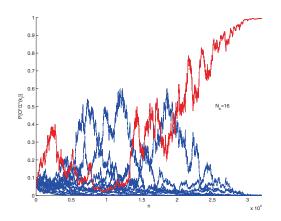

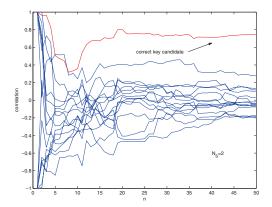

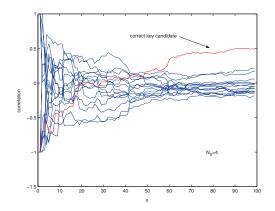

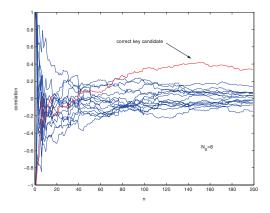

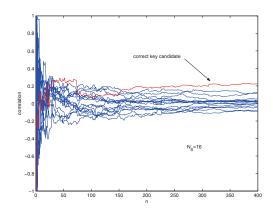

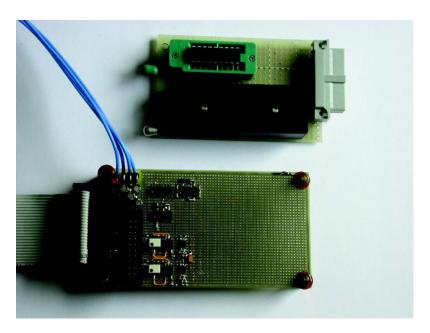

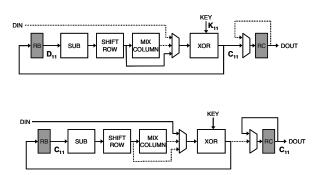

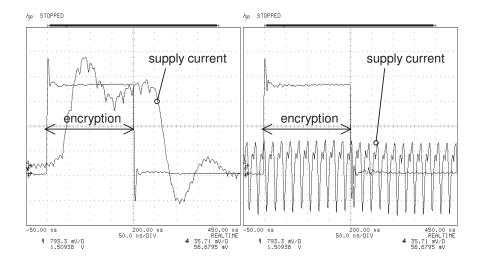

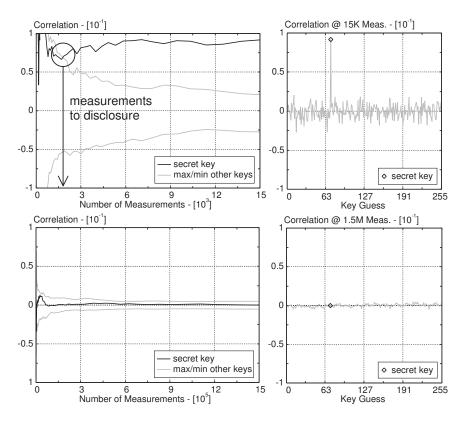

As an illustration, consider the upper plots of Figures 2 and 3 that show DPA attacks on two test cards, one with a protected DES implementation, and another with a protected AES implementation. The target of both attacks was the bit 0 of s-box 1 in round one. The differential samples were obtained by switching off the RNGs of the test cards ( $\nu=1$ ). Both plots show peaks at points in time when the masked s-box output bit leaks. Note that the differential trace from the AES implementation contains less peaks compared to the DES implementation due to the lower contamination properties of AES.

The first step in the profiling stage is to perform exhaustive DPA attacks on the test card using as many samples as possible. In a card with a biased RNG, where the mask is not perfectly random, such an attack will succeed since the

<sup>&</sup>lt;sup>2</sup> We make this simplifying assumption just for the sake of exposition, the attacks would work if bad RNG has different biases for different bits in a random byte.

<sup>&</sup>lt;sup>3</sup> We assume other countermeasures, such as the desynchronization of side channel samples due to random wait states etc., have been removed using signal processing.

DPA prediction of an algorithmic bit (e.g., s-box output bit  $s(x \oplus k)$ ) would be correlated with the masked value of that bit. A successful DPA attack will give us the subkey k (in fact we will get all the subkeys) and also reveal the points of time  $t^*$  when targeted masked algorithmic bit (e.g., masked s-box output bit  $s(x \oplus k) \oplus m$ ) leaks.

The second step of the profiling phase is to create single-bit templates based on each of the DPA attacks. For each DPA attack, the adversary builds a pair of templates for the masked bit being 0 and 1 by using the collected samples at the points where the DPA peaks appear. It may seem that building the template pairs will require that the adversary knows which of the N collected samples have the masked bit 0 and which have the masked bit 1. This is not possible in general, unless the RNG is completely broken in a known way (e.g., fixed at 0). Instead the adversary blindly assumes that the bit is exactly the same as the DPA prediction and builds the templates anyway.

Clearly, if the RNG is not fixed at 0, but has a probability  $\nu$  of outputing a 0 bit, the templates built by an adversary have significant errors. For example when  $\nu > 0.5$ , then the 0-bit template will be built using roughly  $\nu * N/2$  samples that are actually 0 samples and roughly  $(1-\nu)*N/2$  samples that are actually 1's. When  $\nu < 0.5$ , then the templates are inverted: the 0 template is built using more 1 samples than 0 samples. Such templates are equally useful since they will consistently predict the bit incorrectly with high probability. When  $\nu = 0.5$ , DPA will not work and the templates as described here cannot be built.

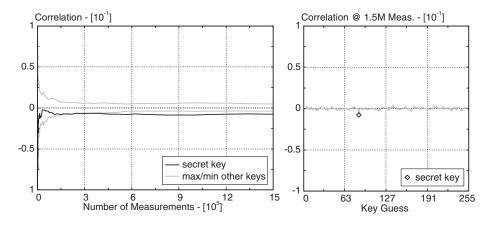

We will show later in the paper that even though significant errors are introduced in the templates when the RNG is very slightly biased, i.e., when  $\nu$  is close to 0.5, if enough signals are used to build these templates, then the performance of the template-enhanced DPA attack is not significantly impacted—the attack works almost as well as an attack using perfect templates ( $\nu = 1$ ).

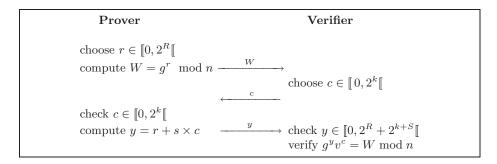

#### 3.2 Hypothesis Testing Phase

Once the adversary has built templates to classify masked s-box output bits in DES or AES using a test device with imperfect RNG, he/she is given a target device to attack that is identical to the test device, except for the fact that its RNG is perfect.

The adversary can make a hypothesis regarding the secret key k used in the target device, and for a particular side channel sample, use the key hypothesis to predict the unmasked output bit  $s(x \oplus k)$ . Furthermore, the adversary can use template classification to predict the masked output bit  $s(x \oplus k) \oplus m$ . These two together can be used to predict the mask bit m itself<sup>4</sup>

$$m = \underbrace{[s(x \oplus k)]}_{\text{prediction}} \oplus \underbrace{[s(x \oplus k) \oplus m]}_{\text{template classification}} \tag{2}$$

Since the mask bit m is an intermediate variable in the algorithm, it will leak at some instances of time in the side channel sample. The idea is to perform

<sup>&</sup>lt;sup>4</sup> We assume that boolean masking is used.

a DPA-like attack on the prediction of m according to the equation above. If the hypothesized value of k is correct, peaks will show up in the corresponding differential trace at points in time when the mask bit m leaks.